# BRE440A<sup>™</sup> RADHARD SOC CPU

The BRE440A Central Processing Unit (CPU) is a fully radiation hardened implementation of the PowerPC 440 processor core in a true System-On-A-Chip (SOC) design, including floating point unit. It meets the requirements for a wide variety of high reliability space and missile applications.

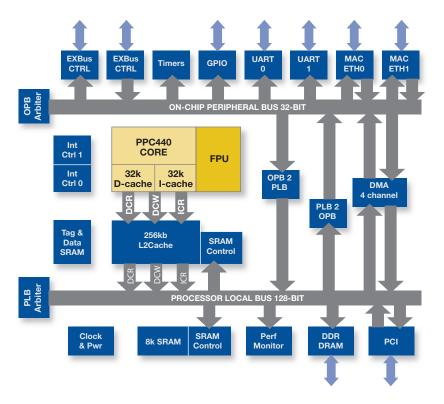

The BRE440A SOC CPU integrates a mix of peripheral controllers by implementing IBM's high speed CoreConnect<sup>™</sup> technology and

contains the PPC440x5 version of the PPC440 core. The embedded processor provides high performance and low power consumption. The BRE440A SOC CPU executes at sustained speeds approaching two instructions per cycle. On-chip peripherals reduce chip count and design complexity in systems and improve system throughput. The 440 core combined with wide peripheral mix provides an ideal foundation for compact systems.

The BRE440A is the next generation of the BRE440 SOC CPU architecture which has extensive flight heritage and is currently on-orbit performing its mission on several spacecraft. This revision is designed to provide the highest level of radiation hardened processing available for spacecraft, missiles, and launch vehicles.

# BRE440A<sup>™</sup> RADHARD CPU

### SPECIFICATIONS

## Features

|                                                              | High Performance IBM PPC440 Core, 2 MIPS/MHz             |

|--------------------------------------------------------------|----------------------------------------------------------|

|                                                              | ANSI/IEEE 754-1985 compliant FPU                         |

| Manufactured on Honeywell 150nm HX5000 Radiation Hardened AS |                                                          |

|                                                              | Superscalar, Dual Issue, 32-bit RISC, Book E Compliant   |

|                                                              | Secure and Trusted Boot with AES256 Encryption (Pending) |

#### Memory

| 32 kByte L1 Instruction & Data Caches                                  |  |

|------------------------------------------------------------------------|--|

| 256 kByte unified L2 Cache (can be configured as general purpose SRAM) |  |

| On-Chip 8 kByte SRAM                                                   |  |

High Bandwidth Main Memory Access with Error Detection and Correction

#### Interfaces

PCI Interface for Peripheral Communication

PCI Arbitration for up to 6 External Peripherals (Clock Distribution)

4 Channel DMA with Scatter/Gather Capability

32-Bit Peripheral Bus with EDAC

32-Bit DDR DRAM Bus with EDAC

External Expansion Bus 2 Ethernet Media Access Controllers

2 UART Ports (16750 Compatible)

JTAG

Radiation Capability

TID >1 MRad; Latch-up immune

SEU >40 Years/Upset (Adams 90% worst case environment)

### Core Clock Frequency

| 300 MHz @ | -55°C to 125°C |

|-----------|----------------|

|-----------|----------------|

330 MHz @ -10°C to 80°C

Typical Power 8.0W @ 330MHz

Typical Power 3.5W @ 240MHz

#### Availability

Available in many of Moog Broad Reach next generation Integrated Avionics Units (IAUs) and board products. Engineering and flight units available Q4 2022

in

Moog Space and Defense

@MoogSDG

Phil Tokeshi, Business Development Manager ptokeshi@moog.com www.moog.com/space

www.moog.com/space

@MoogSDG

@MoogSDG

Equipment described herein falls under the jurisdiction of the EAR and may require US Government Authorization for export purposes. Diversion contrary to US law is prohibited.

© 2021 Moog, Inc. All rights reserved. Product and company names listed are trademarks or trade names of their respective companies.